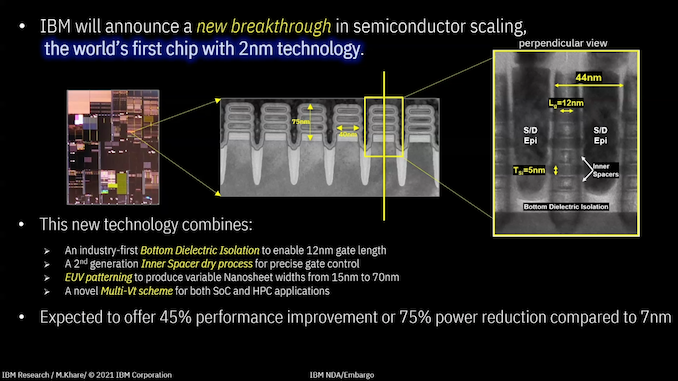

Каждое десятилетие – это десятилетие, которое проверяет пределы закона Мура, и это десятилетие ничем не отличается. С появлением технологии Extreme Ultra Violet (EUV) сложность методов создания нескольких паттернов, разработанных на предыдущих технологических узлах, теперь может быть применена с более высоким разрешением, которое обеспечивает EUV. Это, наряду с другими более техническими улучшениями, может привести к уменьшению размера транзистора, открывая будущее полупроводников. С этой целью сегодня IBM объявляет о создании первого в мире 2-нанометрового узлового чипа.

Имена для узлов

Чтобы прояснить здесь, хотя технологический узел называется «2 нм», ничто в размерах транзистора не напоминает традиционное ожидание того, что может быть 2 нм. Раньше этот размер был эквивалентной метрикой для размера 2D-элемента на кристалле, например 90 нм, 65 нм и 40 нм. Однако с появлением конструкции 3D-транзисторов с FinFET и другими, название технологического узла теперь является интерпретацией конструкции «эквивалентного 2D-транзистора».

Некоторые из функций этого чипа, вероятно, будут иметь низкие однозначные числа в реальных нанометрах, например, слои защиты от утечки ребер транзистора, но важно отметить несоответствие в том, как в настоящее время называются узлы процесса. Часто аргумент сводится к тому, что плотность транзисторов является более точным показателем, и IBM делится с нами этим.

Плотность транзистора

В сегодняшнем заявлении говорится, что разработка IBM 2-нм процессоров улучшит производительность на 45% при той же мощности или на 75% энергии при той же производительности по сравнению с современными 7-нм процессорами. IBM стремится указать, что это было первое исследовательское учреждение, продемонстрировавшее 7 нм в 2015 году и 5 нм в 2017 году, последнее из которых перешло с FinFET на технологии нанолистов, которые позволяют более точно настраивать характеристики напряжения отдельных транзисторов.

IBM заявляет, что с помощью этой технологии можно разместить «50 миллиардов транзисторов на микросхеме размером с ноготь». Мы обратились в IBM с просьбой разъяснить, каков размер ногтя, учитывая, что внутренне мы придумывали числа от 50 квадратных миллиметров до 250 квадратных миллиметров. В пресс-службе IBM заявили, что размер ногтя в данном контексте составляет 150 квадратных миллиметров. Таким образом, плотность транзисторов IBM составляет 333 миллиона транзисторов на квадратный миллиметр (MTr / мм2).

Для сравнения:

| Пиковая заявленная плотность транзисторов (MTr / мм2) | ||||

| АнандТех | IBM | TSMC | Intel | Samsung |

| 22 нм | 16,50 | |||

| 16нм / 14нм | 28,88 | 44,67 | 33,32 | |

| 10 нм | 52,51 | 100,76 | 51,82 | |

| 7 нм | 91,20 | 237,18 * | 95,08 | |

| 5 нм | 171,30 | |||

| 3 нм | 292,21 * | |||

| 2 нм | 333,33 | |||

| Данные Wikichip, разные фабрики могут иметь разные методологии подсчета. * Расчетная плотность логики |

||||

Как видите, у разных литейных заводов разные официальные названия с разной плотностью. Стоит отметить, что эти значения плотности часто указываются как пиковые плотности для библиотек транзисторов, где площадь кристалла является пиком, а не масштабирование частоты – часто самые быстрые части процессора в два раза меньше, чем эти числа, из-за проблем с питанием и температурой. .

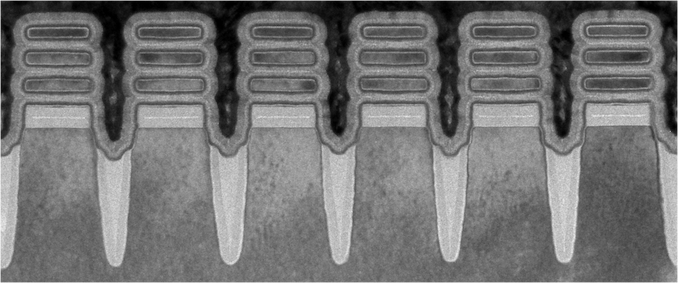

Что касается перехода к транзисторам Gate-All-Around / нанолистам, то, хотя это явно не указано IBM, изображения показывают, что этот новый 2-нм процессор использует трехступенчатую конструкцию GAA. Samsung представляет GAA на 3 нм, а TSMC ожидает 2 нм. Мы полагаем, что Intel, напротив, представит некоторую форму GAA на своем 5-нм техпроцессе.

В 3-стековом GAA IBM используется высота ячейки 75 нм, ширина ячейки 40 нм, а отдельные нанолисты имеют высоту 5 нм, разделенные друг от друга на 5 нм. Шаг поликлинового затвора составляет 44 нм, а длина затвора – 12 нм. IBM заявляет, что в ее конструкции впервые используются нижние диэлектрические изоляционные каналы, обеспечивающие длину затвора 12 нм, и что ее внутренние прокладки представляют собой сухую технологическую конструкцию второго поколения, которая помогает в разработке нанолистов. Это дополняется первым использованием EUV-паттерна на частях процесса FEOL, что позволяет использовать EUV на всех этапах проектирования критических слоев.

Пользователи могут задаться вопросом, почему мы слышим, что IBM является первой компанией, использующей 2-нм чип. IBM – один из ведущих мировых исследовательских центров по будущим полупроводниковым технологиям, и, несмотря на то, что у IBM нет собственных литейных предложений, IBM вместе с другими разрабатывает интеллектуальную собственность для своих производственных предприятий. IBM продала свое производство GlobalFoundries с 10-летним партнерским соглашением еще в 2014 году, и IBM также в настоящее время работает с Samsung и недавно объявила о партнерстве с Intel. Несомненно, последние двое будут сотрудничать с IBM на каком-то уровне в связи с этой новой разработкой, чтобы обеспечить ее жизнеспособность в их собственной производственной цепочке.

Исследовательский центр IBM в Олбани

Никаких подробностей о 2-нм тестовой микросхеме предоставлено не было, хотя на данном этапе это, вероятно, будет упрощенная тестовая машина SRAM с небольшой логикой. Изображения 12-дюймовых пластин демонстрируют различные варианты дифракции света, что, вероятно, указывает на множество тестовых примеров, подтверждающих жизнеспособность технологии. IBM заявляет, что в тестовом проекте используется схема с несколькими виртуальными терминалами для демонстрации высокопроизводительных и эффективных приложений.

Чип был разработан и изготовлен в исследовательском центре IBM в Олбани с чистой комнатой площадью 100 000 кв. Футов. Цель этой возможности – использовать обширный портфель патентов и лицензий IBM для сотрудничества с партнерами.

У нас есть ряд вопросов к экспертам IBM, которые ждут ответа. У нас также есть активное приглашение посетить, когда мы снова сможем путешествовать.